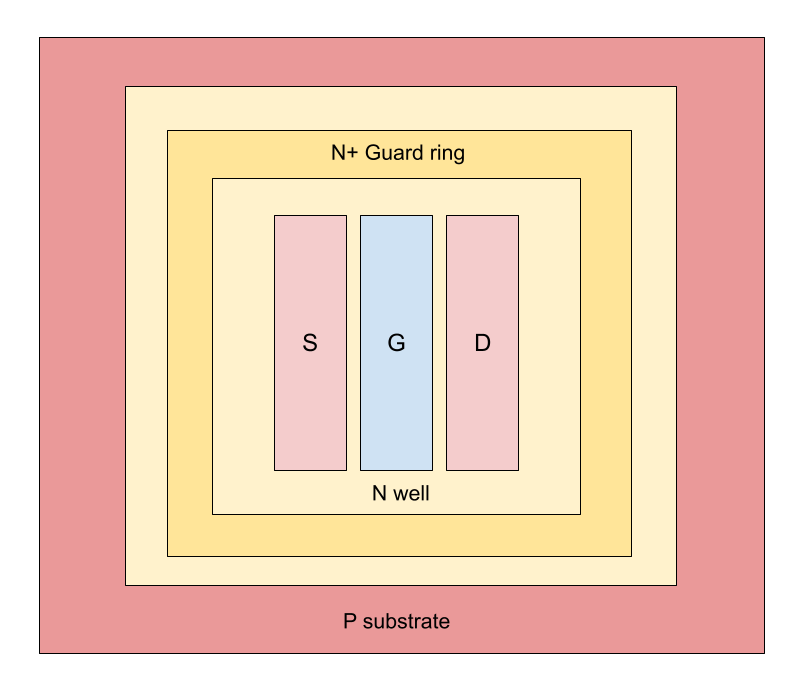

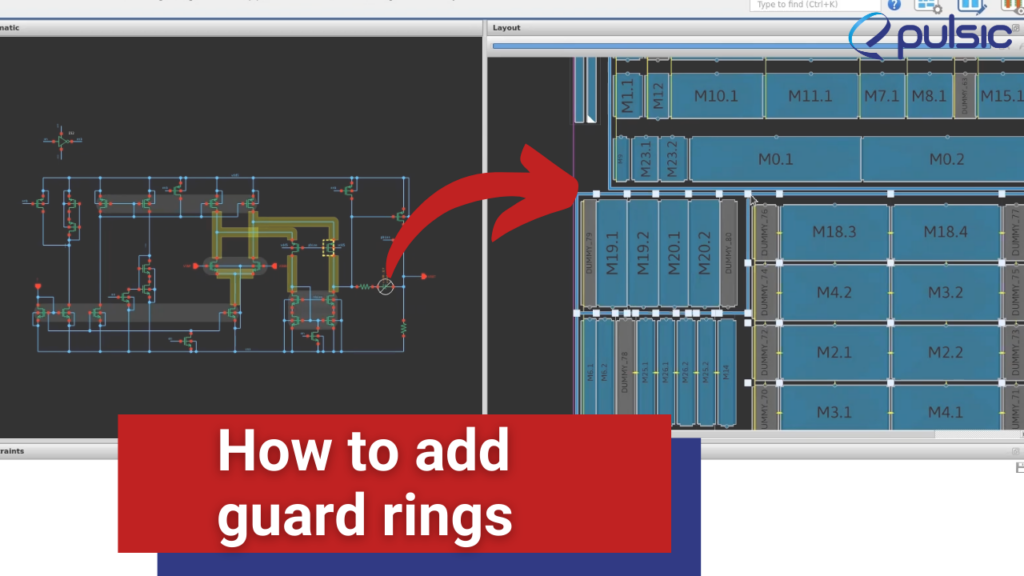

NAND2 (left) and row_cap (right) showing guard ring structure-row_cap... | Download Scientific Diagram

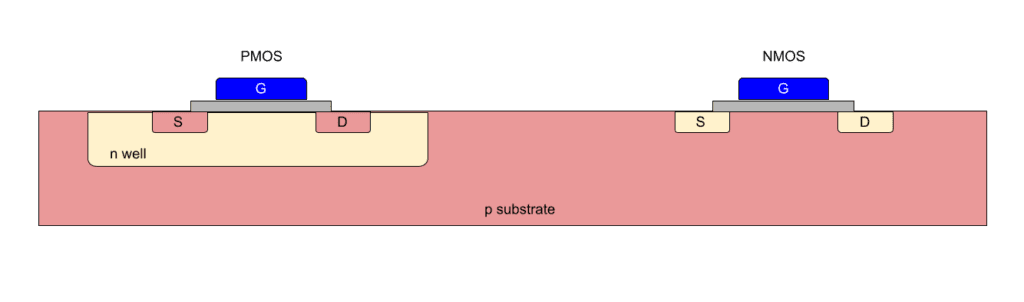

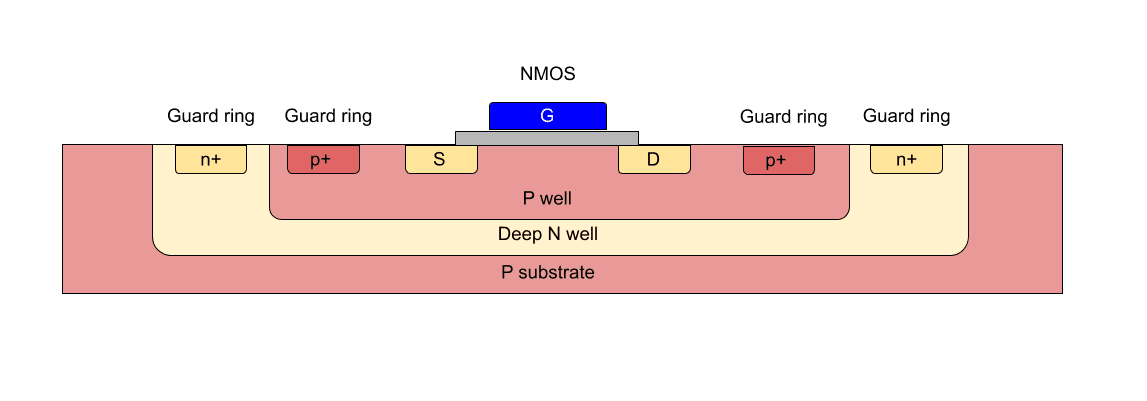

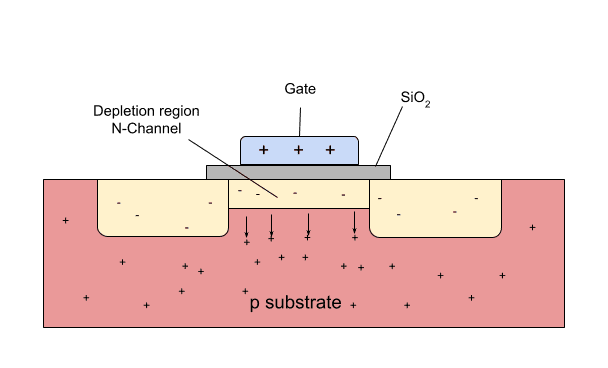

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology - ScienceDirect

Guard rings: Structures, design methodology, integration, experimental results, and analysis for RF CMOS and RF mixed signal BiCMOS silicon germanium technology - ScienceDirect

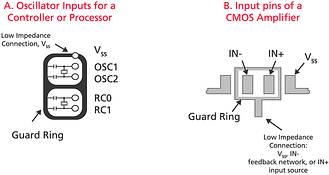

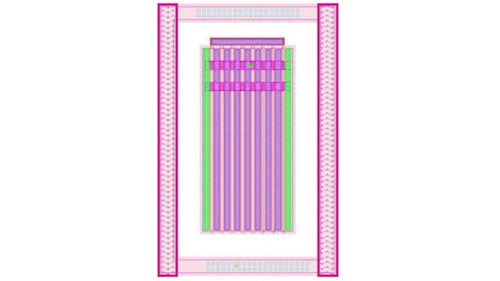

![PDF] Automatic methodology for placing the guard rings into chip layout to prevent latchup in CMOS IC's | Semantic Scholar PDF] Automatic methodology for placing the guard rings into chip layout to prevent latchup in CMOS IC's | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/fe254521aef5b507685c80a88fe097713fbec75d/1-Figure1-1.png)

PDF] Automatic methodology for placing the guard rings into chip layout to prevent latchup in CMOS IC's | Semantic Scholar

Figure 1 from Improved latch-up immunity in junction-isolated smart power ICs with unbiased guard ring | Semantic Scholar